臺積電攜手美國客戶共研3D封裝技術(shù),引領(lǐng)計算機軟硬件協(xié)同革新

全球半導(dǎo)體制造巨頭臺積電宣布與美國核心客戶深化合作,共同推進先進3D封裝技術(shù)的研發(fā),并計劃于2022年實現(xiàn)量產(chǎn)。這一戰(zhàn)略舉措不僅標(biāo)志著半導(dǎo)體制造工藝向立體集成邁出關(guān)鍵一步,也將對計算機硬件設(shè)計與軟件開發(fā)模式產(chǎn)生深遠影響,推動整個產(chǎn)業(yè)鏈的技術(shù)協(xié)同創(chuàng)新。

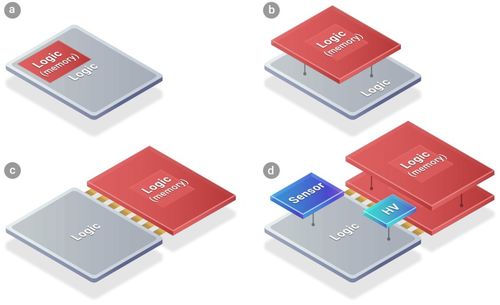

在硬件層面,3D封裝技術(shù)通過垂直堆疊芯片,大幅提升了晶體管密度與互聯(lián)效率。傳統(tǒng)平面封裝受限于物理空間,而3D封裝允許將處理器、內(nèi)存、傳感器等不同功能的芯片像“高樓”一樣層層疊加,實現(xiàn)更短的數(shù)據(jù)傳輸路徑與更低的功耗。臺積電此次研發(fā)重點包括硅通孔(TSV)、微凸塊(Micro-bump)等核心工藝,旨在突破散熱與信號完整性等瓶頸。量產(chǎn)后,預(yù)計將率先應(yīng)用于高性能計算、人工智能加速器及移動設(shè)備芯片,使計算機硬件在有限體積內(nèi)釋放更強算力。

與此軟件生態(tài)也需同步演進以適配3D封裝帶來的架構(gòu)變革。硬件層級的立體集成要求操作系統(tǒng)、編譯器及開發(fā)工具鏈能夠識別并優(yōu)化多層芯片的協(xié)同工作。例如,軟件需動態(tài)調(diào)度任務(wù)至不同堆疊層,以平衡功耗與性能;內(nèi)存管理算法也需重構(gòu),以利用3D封裝帶來的高帶寬內(nèi)存優(yōu)勢。臺積電與客戶合作中,已開始探索軟硬件協(xié)同設(shè)計框架,通過仿真平臺提前驗證芯片堆疊的軟件兼容性,減少未來量產(chǎn)后的適配成本。

從行業(yè)視角看,此次合作凸顯了全球半導(dǎo)體產(chǎn)業(yè)鏈的深度融合。美國客戶在芯片設(shè)計領(lǐng)域的領(lǐng)先能力,結(jié)合臺積電的制造專長,加速了3D封裝從實驗室走向商業(yè)化。這一技術(shù)突破將進一步鞏固臺積電在先進制程的霸主地位,并為下游計算機廠商提供更靈活的硬件方案——從數(shù)據(jù)中心服務(wù)器到邊緣計算設(shè)備,均可通過定制化3D封裝實現(xiàn)性能躍升。

2022年量產(chǎn)計劃若順利落地,或?qū)⒁l(fā)連鎖創(chuàng)新:硬件上,更多廠商可能跟進研發(fā)異構(gòu)集成芯片;軟件上,開源社區(qū)與商業(yè)公司需加快適配新架構(gòu)。臺積電此番布局,不僅是一場制造工藝的升級,更是推動計算機軟硬件從“平面時代”邁向“立體時代”的關(guān)鍵引擎,為數(shù)字經(jīng)濟注入新的動能。

如若轉(zhuǎn)載,請注明出處:http://www.jhjsx.cn/product/30.html

更新時間:2026-02-24 03:53:52